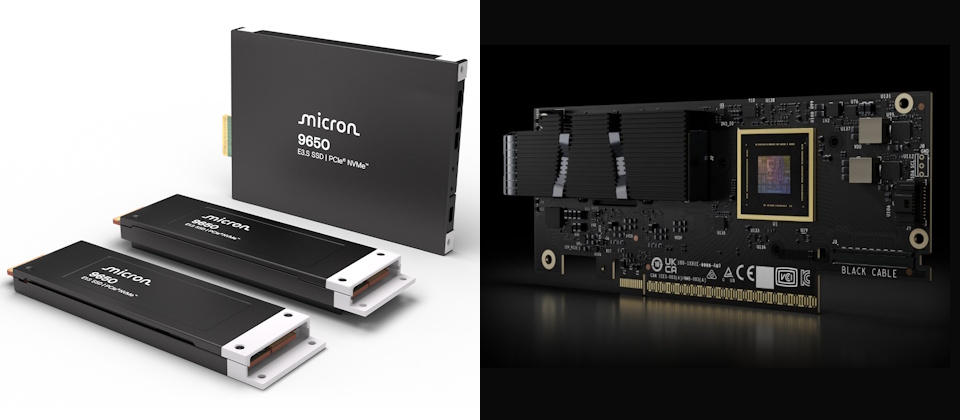

圖片來源/Micron、Nvidia

自2003年迄今,PCIe一直扮演著伺服器核心I/O架構的角色,作為CPU與GPU、網路卡、SSD等周邊裝置之間的傳輸通道,幾乎所有周邊裝置或其他I/O介面,都是直接或間接透過PCIe的介接,來與運算核心連結。隨著CPU與周邊裝置速度的提高,PCIe也隨之持續進化,以便為處理器與周邊裝置提供更高的傳輸頻寬。

目前市場上的PCIe介面應用主流,仍是問世多年的PCIe 4.0與PCIe 5.0——規格分別於2017與2019年發布。不過新一代PCIe規格的應用與發展,近幾個月來終於出現重要進展,第一批PCIe 6.0規格的周邊產品正式上市,而PCIe 7.0與PCIe 8.0的規格制定工作,也有具體的成果。

PCIe 6.0開始進入產品化

相較於過去幾個PCIe世代,PCIe 6.0的產品化腳步顯得格外緩慢。

PCIe 4.0與PCIe 5.0都是在規格發布1、2年內,就誕生第一批應用新介面的SSD與周邊產品,反觀PCIe 6.0在2022年初發布規格後,經過三年多的發展,仍只停留在開發測試用設備,以及交換器晶片、中介片(Interposer)等元件層次,遲遲沒有應用到完整產品上。

PCIe 6.0產品應用停滯的情況,直到2025年中才終於出現轉機。在2025年5月底的Computex會場中,多家SSD廠商都向我們表示PCIe 6.0 SSD產品已在開發測試中。有騰科技(UTRAN)也在會場上展出PCIe 6.0開發測試設備,由主機端介面卡、外接擴充機箱構成的PCIe 6.0開發測試設備,可提供外接的PCIe 6.0 x16埠,用於PCIe設備的測試。

Computex會場上見到國內廠商展出PCIe 6.0測試設備,我們可將其看做是第一批PCIe 6.0周邊產品即將問世的信號,顯示已出現相當強勁的PCIe 6.0相關產品測試需求,才促使有騰科技等廠商推出測試設備,也讓我們對PCIe 6.0產品的實際推出有進一步的期待。

果不其然,時隔2個月後,美光(Micron)推出首款支援PCIe 6.0的SSD產品9650系列。

與此同時,Nvidia也在2025下半年陸續發布採用PCIe 6.0介面的新世代網路卡產品,包括ConnectX-8、ConnectX-9與BlueField-4等。

相較於美光上一代採用PCIe 5.0的9550系列SSD,9650系列SSD憑藉PCIe 6.0提供的加倍傳輸頻寬,將最大傳輸速率從14GB/s一舉提高到28GB/s(循序讀取)。

而比起Nvidia上一代基於PCIe 5.0介面的ConnectX-7與BlueField-3,ConnectX-8、ConnectX-9與BlueField-4等新網路卡產品,也藉由PCIe 6.0介面,將400 Gb與800 Gb傳輸通道帶進GPU運算平臺上。

不過,除了前述先驅產品外,要讓PCIe 6.0應用環境完整成形,還是得有伺服器平臺的支援,這方面我們只能等待Intel Diamond Rapids與AMD Venice處理器平臺,能按時於2026年推出。

.png)

第一批PCIe 6.0周邊設備問世

在PCIe 6.0規格發布過後,等待了3年半,第一批支援PCIe 6.0的產品終於在2025年下半年陸續發表,包括美光的9650系列SSD,以及Nvidia的ConnectX-8、ConnectX-9與BlueField-4等網路卡與DPU卡產品。圖片來源/Micron、Nvidia

PCIe 7.0與8.0的規格發展

儘管PCIe 6.0的產品化應用才剛剛起步,負責規格制定的PCI-SIG組織,已經在推動下一代的PCIe 7.0與PCIe 8.0規格發展。

記取了在PCIe 3.0上停滯過久的教訓,自PCIe 4.0起,PCI-SIG的策略是每3年更新一代規格,在2022年推出PCIe 6.0之後,接著PCIe 7.0與PCIe 8.0將分別於2025與2028年發布。

在PCIe 7.0方面,PCI-SIG於2023年6月發布最早的0.3版規格草案,接著在2024年4月發布0.5版規格草案,然後在2025年一口氣加快規格制定進度,先後於1月與3月發布0.7版與0.9版(前者為完整版草案,後者為最終草案),然後在2025年6月發布最終版PCIe 7.0規格,主要規格特性包括:

沿用PCIe 6.0開始使用的PAM4信號編碼技術,但可提供較PCIe 6.0高出1倍的128 GT/s原始位元速率(Raw Bit Rate),在x16通道下可實現512GB/s的雙向傳輸速率,並在更高的速率下確保通道參數、傳輸距離、可靠性與低延遲目標,同時也須具備與前幾代PCIe的相容性,以及改善功耗效率。

接著PCI-SIG還預定在2027年推出驗證PCIe 7.0標準合規性(Compliance)的計畫,預期支援PCIe 7.0的產品也會在此之後發布。

在PCIe 8.0方面,PCI-SIG在2025年8月發表PCIe 8.0規格的展望,稍後在9月中旬宣布已向會員發布0.3版PCIe 8.0規格草案,預計2028年完成規格制定,預期的目標包括:

較PCIe 7.0高出1倍的256 GT/s原始位元傳輸速率,搭配x16通道可實現1 TB/s的雙向傳輸速率;將評估新的連接器(Connector)技術;透過前向錯誤糾正(Forward Error Correction,FEC)實現低延遲目標;確保可靠性,以及與前幾代PCIe的相容性,另外還將透過協定增強功能(Protocol Enhancements),來提高可用頻寬,以及強調應用低功耗的技術。

就技術來看,PCIe 7.0與8.0都沿用了PCIe 6.0的基本架構,而與PCIe 5.0以前有較大的區別,包括以PAM4信號編碼取代早先PCIe的NRZ編碼,藉此在相同頻率內承載兩倍資料,但為彌補PAM4編碼較高的錯誤率,搭配前向糾錯技術以確保資料完整性。另外,它們還以固定大小的資料流控制單元(Flow Control Unit),取代先前世代PCIe介面使用的可變大小事務層資料封包(Transaction Layer Packet,TLP),確保高速傳輸下的可靠性。

熱門新聞

2026-02-06

2026-02-06

2026-02-06

2026-02-06

2026-02-09

2026-02-09