圖片來源/CXL Consortium

以打破跨裝置記憶體資源運用藩籬,從而改善伺服器記憶體效能與擴充瓶頸為訴求的CXL(Compute Express Link)技術,日前又有新發展。

CXL聯盟於不久前的2025年11月底,發表新的CXL 4.0版規格,引進基於PCIe 7.0的新底層,結合多項新功能,擴展傳輸頻寬與連接能力。

自從2022年8月發布CXL 3.0以來,CXL聯盟大致是以每年一次的周期,持續更新CXL規格。

先是在2023年11月推出的CXL 3.1,接著是2024年12月發布的CXL 3.2,然後便是日前推出的CXL 4.0。

每次CXL規格更新,各有不同的側重點,例如,CXL 3.1重點放在底層網路連接架構的改進,以便能建構規模更大的CXL應用環境,CXL 3.2的重點則是提高監控管理與安全性。

至於新推出的CXL 4.0,更新重點則圍繞著提高傳輸頻寬,與裝置、主機之間的連接能力(Connectivity)。

CXL 4.0的新功能

CXL 4.0對於傳輸頻寬與連接能力的強化,是建立在底層實體傳輸通道,以及一系列新軟體功能上。

CXL的實體傳輸通道是嫁接在PCIe上,最早的CXL 1.x與2.0是基於PCIe 5.0,CXL 3.0升級為PCIe 6.0,從而將傳輸通道頻寬提升1倍。而到了CXL 4.0,隨著稍早前PCIe 7.0正式發布,也順勢將底層傳輸通道升級為PCIe 7.0,將頻寬又再提升1倍。

CXL 4.0的新功能:聚合連接埠頻寬

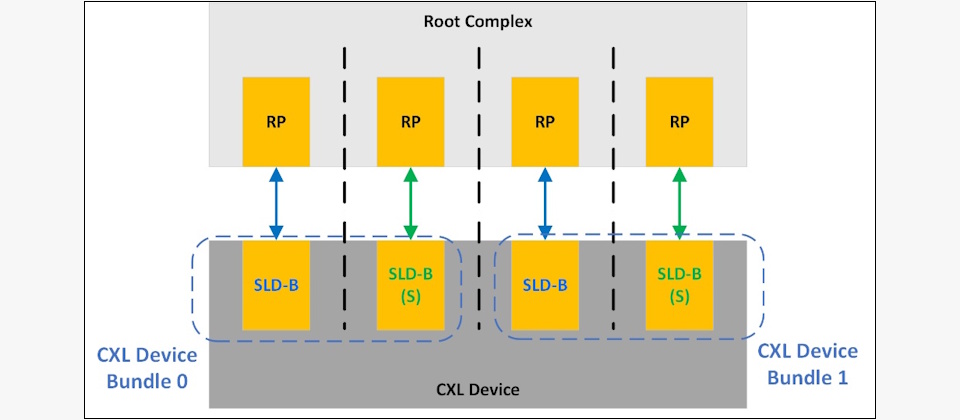

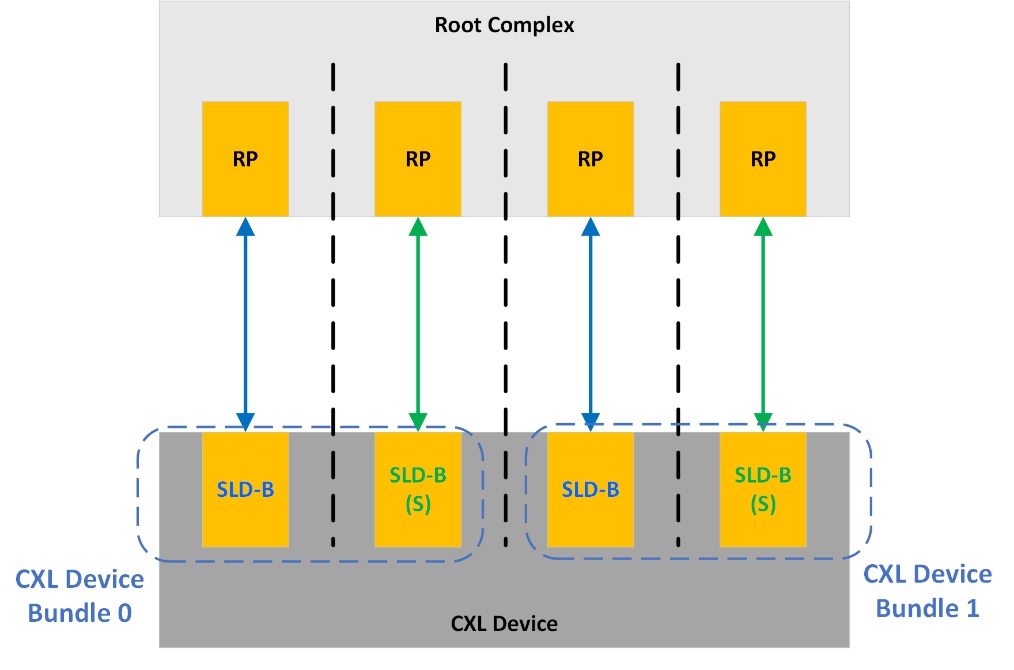

CXL 4.0的目標是提高傳輸頻寬,除了引進新的PCIe 7.0通道作為底層外,還新增連接埠捆綁(Bundled Ports)的新功能,可將多個CXL設備連接埠聚合為1個邏輯連接埠,讓系統識別為單一設備,並藉此提高傳輸頻寬。圖片來源/CXL Consortium

除了憑藉PCIe 7.0所帶來的傳輸頻寬提升外,CXL 4.0還引進原生x2鏈結寬度(Native x2 width),支援4個重定時器(Retimer),以及連接埠捆綁(Bundled Ports)等新功能,進一步改善頻寬與連接彈性。

鏈結寬度是指CXL連接時使用的資料通道(lane)數量,先前的CXL支援x4、x8與x16寬度(標準是使用x16),只有在故障、降級模式下才會使用備用的x1與x2寬度,而自CXL 4.0起則能在一般傳輸中使用x2寬度,從而可增加整體的連接數量。

而隨著CXL 4.0引進傳輸速率提高的PCIe 7.0,為了克服連帶而來的信號品質與傳輸距離問題,CXL 4.0也透過支援4個重定時器,藉此改善PCIe信號品質,因傳輸距離與資料傳輸速率增加而下降的情況,藉此擴展CXL連接能力,在擴大連接數量與距離時,仍能確保信號完整性,從而更好的支援多機櫃之間的連接應用,也有助於改進大規模環境中的連接能力,幫助CXL技術在大型環境中的應用擴展。

至於連接埠捆綁功能,則能將多個CXL實體連接埠聚合為1個邏輯埠,藉此改善傳輸頻寬與連接靈活性。

但另一方面,由於CXL 4.0的底層實體傳輸架構,是基於新推出的PCIe 7.0,所以實際進入應用環境的腳步,也被綁在CXL 7.0上,會受到PCIe 7.0產品化的時程制約,預期需等到PCIe 7.0應用環境在2027年以後逐步成形,CXL 4.0才能隨之進入實用化。

熱門新聞

2026-02-09

2026-02-06

2026-02-09

2026-02-09

2026-02-09

2026-02-09

2026-02-06