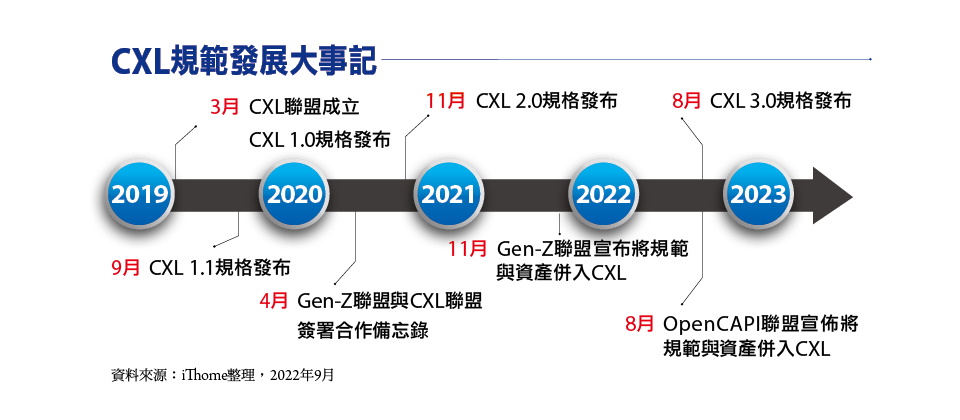

為了克服主機CPU記憶體傳輸通道與頻寬成長受限問題,過去幾年以來,市面上出現了一系列處理器記憶體互連共享技術,其中,CXL雖然問世較晚,但目前最被看好,而一些較早發展的同類技術策略聯盟,包括Gen-Z、OpenCAPI等,都於近期先後被CXL吸收,可望讓CXL成為這個領域的共通標準。

CXL技術發展的歷史可以追溯到2019年3月,在Intel主導下,號召阿里巴巴集團、Cisco、Dell、Facebook(Meta)、Google、HPE、華為、微軟等廠商,成立了CXL聯盟(CXL Consortium),共同發展與推廣這個高速介面新標準。

接下來,又有更多廠商參與這個陣營,以目前CXL聯盟董事會(Board of Directors)而言,除了前述9家創始成員,還有AMD、Arm、IBM、美光與Nvidia;以貢獻者(Contributors)身分參與CXL聯盟的廠商,則有Ericsson、富士通、新華三、Hitachi、浪潮、Kioxia、聯想、Oracle、高通、Seagate、SK hynix、VMware、WD等,超過60家,幾乎囊括當前主要的處理器、伺服器、網通、儲存供應商。

CXL規範的發展歷程

CXL規範迄今一共發展了3個世代,一共4個主要版本,包括1.0版、1.1版、2.0版、3.0版。

CXL 1.0與1.1

最早的CXL 1.0版規範發布於2019年3月,以PCIe 5.0作為傳輸介面的實體層,可讓主機CPU透過CXL提供的快取一致性協定(cache coherent protocol),存取周邊加速運算裝置上的共享記憶體,這也就是後來所稱的Type 2應用模式。

CXL 1.1版緊接著在2019年9月發布,在1.0版的基礎上,提供周邊裝置層級的記憶體擴展能力(device-level memory expansion),而這也就是後來所稱的Type 3應用模式,以及一致性加速器模式(coherent accleartor mode),即Type 1模式,讓CXL的應用形態更加多元。

CXL 2.0

一年多之後,CXL 2.0版於2020年11月推出,而這個版本最重要的規格內容更新,是支援CXL裝置間的交換連接(switching)功能。

先前的CXL 1.x版中,每個周邊裝置同時間只能由1個主機CPU存取,CPU與周邊裝置之間是一對一連結;到了CXL 2.0,可透過虛擬CXL交換器(Virtual CXL Switch)的中介,讓主機CPU與周邊裝置之間構成多對多的連接,多個支援CXL 1.x或CXL 2.0的周邊裝置,可同時連結多個支援CXL 2.0的主機CPU,藉此將多個裝置的記憶體結合為分散式的共享記憶體池。

CXL 2.0另外也新增確保資料完整性與加密的機制,可支援硬體式安全協定引擎、硬體式信任根(hardware root of trust)等。不過,CXL 2.0的實體層依舊是採用PCIe 5.0,因而傳輸頻寬仍與CXL 1.x相同。

CXL 3.0

今年8月,CXL 3.0版規範正式發布,最重要特色是實體層改用基於PAM-4編碼的PCIe 6.0,從而將傳輸頻寬提升一倍。另外,CXL 3.0也進一步強化交換連接架構,可透過一系列新功能,例如多層式交換(multi-level switching)、主機多重類型周邊裝置連接,讓CXL裝置組成規模更大、更複雜的交換連接架構,並結合強化的硬體一致性機制,提供更彈性的記憶體池共享存取應用。

CXL 3.0還有其他的新功能,包括:周邊裝置間的點對點訊息傳輸(Peer-to-Peer messaging),也就是在周邊裝置之間,提供一種不經由CPU的DMA傳輸架構,另外,還配合PCIe 6.0的採用,支援256 bytes大小的流量控制單元(FLIT)等。

CXL發展的階段區分

我們可以依據CXL規範各個版本的功能演進,將目前CXL協定的發展分為3個階段:

一開始的CXL 1.x版,初步實現了主機CPU共享周邊裝置記憶體的目的,但兩者之間只能一對一的直連,運用彈性受到較大的限制。

接下來的CXL 2.0版,引進了交換連接架構,可以讓多個周邊裝置與多個主機CPU彼此互連,從而構成跨多個裝置、多臺機箱的記憶體池。

而且,每個CXL 2.0周邊裝置,還能切割為多個邏輯裝置(Logical Devices),藉此將自身記憶體的不同區域(memory region)動態分派給最多16個主機CPU存取,大幅改善CPU與周邊裝置間的連接彈性。

CXL 2.0也新增完整性與資料加密機制(Integrity and Data Encryption,IDE)改善了安全性。

到了最新的CXL 3.0,進一步擴展了傳輸效能與交換連接能力。

在傳輸效能方面,CXL 3.0透過引進PCIe 6.0,提供加倍的傳輸頻寬。

在交換連接能力方面,CXL 3.0藉由新增多層交換連接架構、CPU端更靈活的周邊裝置連接能力,以及改進的多重存取能力,可以組成更複雜、龐大,也更彈性的CXL連接環境,

先前CXL 2.0只支援單層的交換連接架構,而CXL 3.0則提供多層的交換連接架構,進而能支援網格(Mesh)、環狀(Ring)等非樹狀的交織(Fabrics)連接架構,並搭配基於連接埠的路由尋址架構(Port Based Routing,PBR),可支援多達4,096個節點,且每個節點可以是主機CPU或周邊裝置,藉此將能組成非常龐大、複雜的CXL連接環境。

此外,對於主機CPU端的根埠(root port)混搭連接不同CXL周邊裝置的限制,CXL 3.0也予以解放,每個主機CPU可同時混搭連接多個不同類型的CXL周邊裝置,相對的,CXL 2.0對主機CPU端同時連接的Type 1與Type 2裝置數量,則有一定的限制。

而在記憶體池的多重存取能力方面,先前CXL 2.0雖然就能提供分散式的記憶體池架構,周邊裝置也能將記憶體分為多個區域,指派給不同主機CPU使用,但是,每個記憶體區域同時只能給1個主機CPU存取;而到了CXL 3.0,可搭配強化的硬體一致性機制,能將周邊裝置的記憶體區域,同時共享給多個主機CPU使用。

CXL規範的組成

基本上,CXL規範是由3個獨立的協定組成:CXL.io,CXL.cache,以及CXLmem(即CXL.memory)。

其中的CXL.io,提供底層傳輸通道與裝置的管理,以PCIe 5.0為基礎,結合一些改進的功能而成;CXL.cache提供周邊設備存取主機CPU記憶體的功能;CXL.mem則提供主機CPU以一致性快取方式,存取周邊裝置記憶體的功能,包括:揮發性與非揮發性的記憶體。整體而言,3種協定可各自獨立運作,也可相互搭配、組合運作。

CXL的3種應用形態

CXL也定義3種周邊裝置應用型態:

Type 1:透過CXL.io與CXL.cache協定運作,適用於那些沒有配置獨立記憶體的特定用途加速裝置,例如,某些智慧型網路卡或影像加速卡,現在可以透過CXL協定來存取主機CPU的記憶體,將這些記憶體分享給這些周邊裝置,作為快取記憶體使用。

Type 2:透過CXL.io、CXL.cache與CXL.mem協定運作,用於自身擁有高效能記憶體(GDDR或HBM記憶體)的通用型加速裝置,如GPU卡,或是基於FPGA、ASIC的加速卡等,可透過CXL協定在這些周邊裝置與主機CPU之間,提供雙向的記憶體共享,既可讓周邊裝置存取主機CPU的記憶體,也能讓主機CPU存取周邊裝置的記憶體。

Type 3:透過CXL.io與CXL.mem協定運作,這類裝置是基於DRAM或儲存級記憶體(Storage Class Memory,SCM)的記憶體擴充板卡,主機CPU可以透過CXL協定,來存取這類記憶體擴充板卡搭載的DRAM,或是非揮發性的SCM記憶體。

以我們的觀點來看,CXL Type 1應用裝置的基本概念,類似CPU內建顯示晶片而能共用系統主記憶體的架構,同樣都可讓周邊裝置使用主記憶體,讓這些周邊裝置免除配置獨立記憶體的需要,區別在於:前者只適用於CPU內建顯示晶片的狀況,CXL則允許任何支援CXL.io與CXL.cache協定的PCIe周邊裝置,使用系統的主記憶體。

而CXL Type 2應用裝置的主要訴求,是藉由共享主機CPU與周邊裝置的記憶體,動態調配兩者的記憶體資源,進而提高系統整體記憶體資源的利用效率。

至於CXL Type 3應用裝置的目的,則是透過記憶體擴充卡,來提高伺服器CPU的可用記憶體頻寬與容量。

CXL的傳輸通道

CXL 1.x與CXL 2.0的實體傳輸鏈路,都是基於PCIe 5.0,一般是使用x16的傳輸通道鏈結規格,也就是32GT/s x16,約等於單向63GB/s或雙向126GB/s的傳輸頻寬。

但CXL也能支援使用x8或x4傳輸通道的分支(bifurcation)連接,也能在降級(Degraded)模式下,使用x2或x1的傳輸通道。

而CXL 3.0的實體傳輸鏈路,則改用PCIe 6.0,相同傳輸通道鏈結下的頻寬,較CXL 1.x/2.0提高一倍。

CXL可望成為主要的規格

%EF%BC%BB%E7%B6%B2%E9%A0%81%E5%85%A7%E6%96%87%E5%9C%961%EF%BC%BDCXL%E8%A6%8F%E7%AF%84%E7%99%BC%E5%B1%95%E5%A4%A7%E4%BA%8B%E8%A8%98.png)

不同的處理器記憶體互連技術,一開始的著眼點有很大差異。例如,IBM主導的CAPI/OpenCAPI,最初是為了讓CPU與AFU(加速功能單元)共享記憶體;CXL與CCIX的目的,則是異質處理器晶片互連(CPU、ASIC、FPGA);至於Gen-Z,則是網狀(Fabrics)連接架構的遠端記憶體存取。

但任何處理器互連技術要在x86伺服器領域發揮作用,顯然都少不了Intel的參與及支持,這也讓Gen-Z、OpenCAPI、CCIX這些沒有Intel參與的技術,在推廣與應用上,難有顯著進展。

雖然CAPI/OpenCAPI已用在IBM Power平臺,但Power平臺的市場影響力有限,不足以成為驅動CAPI/OpenCAPI進一步發展與普及的力量。事實上,任何伺服器相關的技術架構,若不能應用到主流的x86平臺,勢必難以成為主流規格。

於是到了最終,仍是由Intel主導的CXL,成為這個領域主導性的規格。

在此之前,原本Gen-Z聯盟曾企圖與CXL「和平相處」,在2020年4月與CXL聯盟簽署合作備忘錄,嘗試將Gen-Z發展成為與CXL互補的規格,讓CXL主導晶片之間的點對點互連,Gen-Z改為著重機箱與機架間的短距離互連(雖然Gen-Z原本也涵蓋了晶片間互連應用)。

然而,CXL聯盟仍逐步進逼。例如,2020年11月發布的CXL 2.0版,將功能擴張到網狀互連領域,也能具備跨機箱遠端記憶體存取能力,此舉形同吸收了Gen-Z主要特色,使得Gen-Z難以為繼。

於是,Gen-Z與CXL聯盟在2021年11月簽署意向書,Gen-Z聯盟決定將規範與資產轉移給CXL,隨後從2022年1月開始解散業務。

到了2022年8月,OpenCAPI聯盟也宣布將規格與資產轉移給CXL聯盟。至於CCIX方面,由於許多成員早已轉向CXL(如AMD、Arm、華為等),所以,實際上也難已有太大發展。

因此,從目前看來,CXL一統處理器記憶體互連技術,應該是大勢已定。

%EF%BC%BB%E7%B6%B2%E9%A0%81%E5%85%A7%E6%96%87%E5%9C%962%EF%BC%BDCXL%E7%9A%84%E5%9F%BA%E6%9C%AC%E6%A6%82%E5%BF%B5.png)

CXL的基本概念

CXL的底層是建立在PCIe 5.0傳輸通道上,利用CXL.io、CXL.cache與CXL.mem等3項協定,讓主機CPU與周邊裝置可以互相存取彼此的DRAM記憶體,從而實現記憶體互連與共享的目的。

%EF%BC%BB%E7%B6%B2%E9%A0%81%E5%85%A7%E6%96%87%E5%9C%963%EF%BC%BDCXL%E7%9A%84%E9%80%A3%E6%8E%A5%E8%83%BD%E5%8A%9B%E6%BC%94%E9%80%B2.png)

CXL的連接能力演進

最早公布的CXL 1.0/1.1規範,只允許主機CPU與周邊裝置一對一直連。

到了CXL 2.0,允許主機與周邊裝置間組成多對多連接的交換網路,大幅提高了CXL裝置連接數量與彈性。

最新的CXL 3.0則進一步提供多層式交換連接,並支援網格式或環狀等非樹狀的交換連接架構,進而可以組成非常龐大的CXL連接環境。

%EF%BC%BB%E7%B6%B2%E9%A0%81%E5%85%A7%E6%96%87%E5%9C%964%EF%BC%BDCXL%E7%9A%843%E7%A8%AE%E5%91%A8%E9%82%8A%E6%87%89%E7%94%A8%E5%BD%A2%E6%85%8B.png)

CXL的3種周邊應用形態

Type 1:適用於自身沒有獨立記憶體的周邊裝置,利用CXL協定將主機CPU的記憶體分享給周邊裝置使用。

Type 2:適用於自身含有高效能記憶體的周邊裝置,利用CXL協定讓主機CPU與周邊裝置相互存取彼此的記憶體,在兩者間動態調整記憶體資源配置

Type 3:適用於內含DRAM或SCM記憶體的記憶體擴充卡,利用CXL協定讓主機CPU存取擴充卡上的記憶體資源,從而提高主機CPU的記憶體容量與頻寬

%EF%BC%BB%E7%B6%B2%E9%A0%81%E5%85%A7%E6%96%87%E5%9C%965%EF%BC%BD%E4%B8%8D%E5%90%8C%E7%89%88%E6%9C%ACCXL%E8%A6%8F%E7%AF%84%E7%9A%84%E5%8A%9F%E8%83%BD%E5%B0%8D%E6%AF%94.png)

熱門新聞

2026-02-11

2026-02-09

2026-02-10

2026-02-11

2026-02-10

2026-02-06

2026-02-10

2026-02-10