英特爾採用Skylake架構的新一代Xeon處理器,在晶片設計架構上將開始採用全新的網格( Mesh)互連架構設計,來取代傳統的環形(Ring)互連設計方式,以改善CPU存取延遲和支援更高記憶體頻寬需求。

英特爾

英特爾前不久才預告採用Skylake微架構的新一代Xeon伺服器處理器推出後,將不再沿用E5和E7的命名方式,而改分成白金、金、銀、銅4個不同等級,今日英特爾更揭露了,下一代Xeon處理器,在晶片設計架構將全部重新設計,改採用全新的網格( Mesh)互連架構取代,做為CPU核心和快取記憶體間存取資料的新途徑,以改善CPU存取延遲,以及支援更高記憶體頻寬的需求,這也是英特爾近年來最大一次的Xeon核心架構大翻新。

英特爾是在自家官網揭露了這項重大訊息,而且不只將在做為旗下Intel Xeon Scalable processors全新系列的新一代Xeon處理器(代號為Skylake-SP)才會採用,甚至也將成為未來發展Xeon伺服器級CPU所使用的全新架構設計。

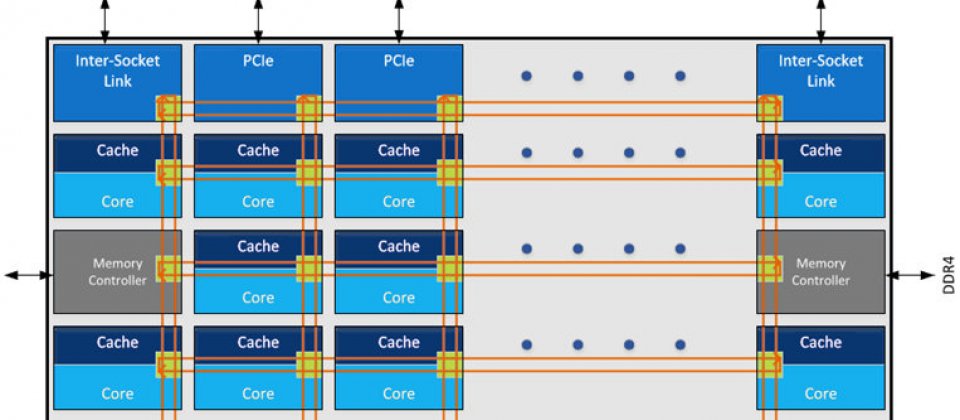

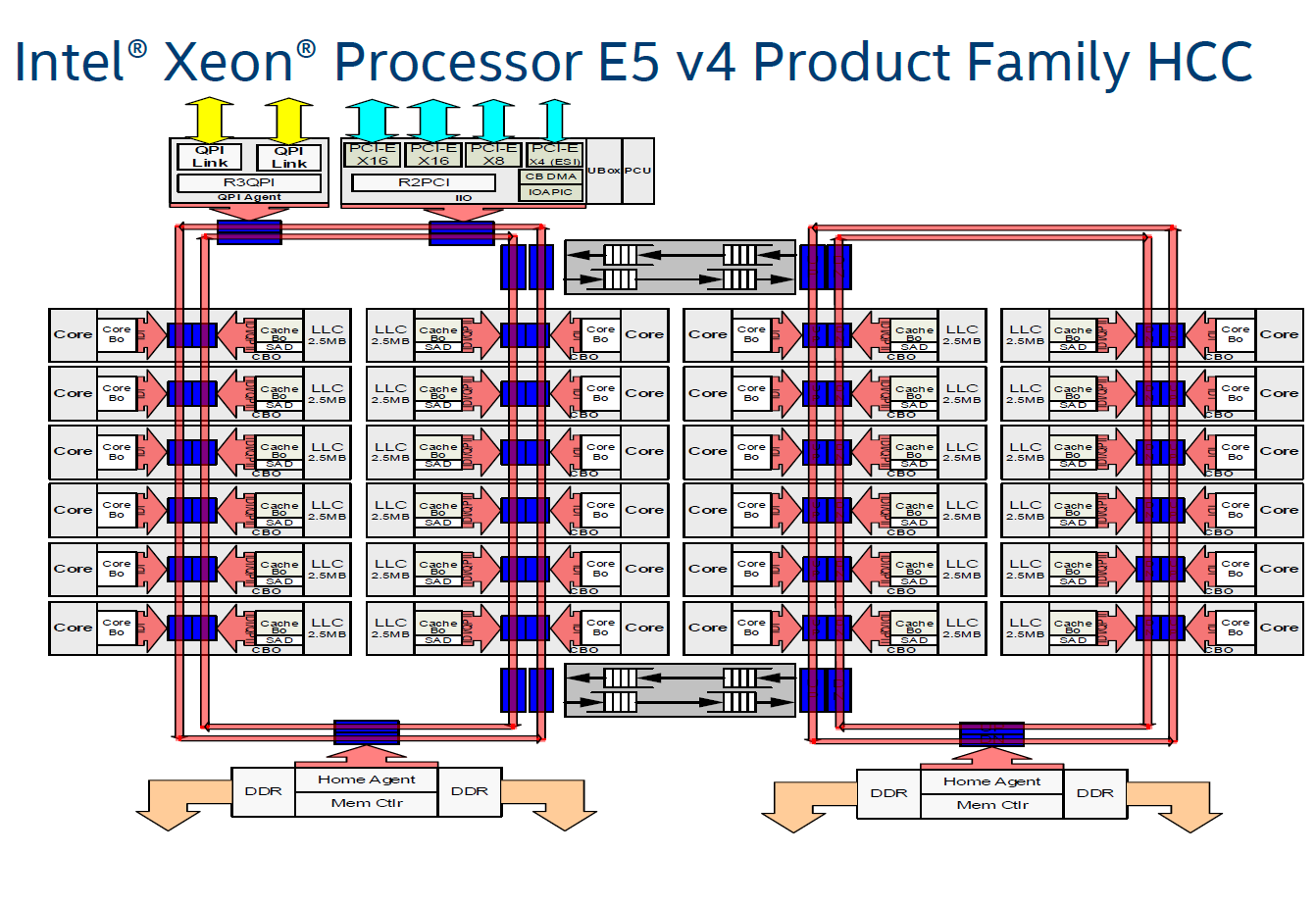

有別於前一代的Broadwell微架構(上圖為HCC(高核心數配置)版本的裸晶片),Xeon處理器晶片上的每顆核心與快取、記憶體控制器及I/O控制器之間,都採用環形(Ring)互連方式,利用每個完整的環狀路徑,來進行資料存取或控制指令傳遞,雖然設計架構上,可以減少CPU存取延遲和降低傳輸成本,不過傳送路徑的選擇有限,一旦核心數增加,若還要能夠很快存取資料,又得支援更高記憶體傳輸頻寬,現有的架構就會開始出現局限。所以英特爾決定重新設計新的晶片架構,以便於能讓CPU具備更高的延展性。

新一代Skylake-SP伺服器處理器將採用全新網格互連架構設計

.png)

英特爾在新一代Skylake-SP微架構晶片設計上,首次開始採用了全新網格互連架構(Mesh Interconnect Architecture)設計方式,從傳統利用環形連接,到了新設計則全面改採用網格互連的方式,來進行資料存取與控制指令的傳送,因為最小單位可以是以每行、每列來連接,所以每顆Skylake-SP 核心、快取、記憶體控制器及I/O控制器之間的路徑選擇變更多元,還可以跨不同的節點互連,以尋找最短的資料傳遞捷徑,即使是加大核心數量時,也能夠維持很快存取資料,並支援更高記憶體頻寬,以及更高速I/O傳輸。

英特爾也提供一張Mesh架構設計概念圖,來說明採用新架構的特色。除了採用新的網狀互連架構外,新一代Xeon處理器架構設計,在對外連接的設計配置上也出現了不少改變,像是做為記憶體通道管理的記憶體控制器,就從原來位在晶片架構底部的位置,被移往晶片中間左右兩側的位置,而做為內部與其他相鄰的處理器連接的系統匯流排,則重新放置在晶片架構最上方左右兩端處。

英特爾也表示,採用了網格互連架構設計的Skylake-SP處理器,還同時具有低功耗的特性,可以允許處理器操作在較低的處理器時脈速度,以及在相對較低的電壓的環境上來進行工作,以便於可以提供更好的效能改善,及提高能源使用效率。

英特爾也形容,採用新的網格互連架構設計,可以使得CPU在進行資料存取或指令傳遞上更有效率,就像是一個經過完整設計的高速公路交流道系統,具備彈性擴充的能力,即使車流量一多,也可以依據車流量多寡,來即時管制進出分散車流量,以減少交通堵塞的情形。

熱門新聞

2026-03-06

2026-03-06

2026-03-06

2026-03-06

2026-03-09

2026-03-09