iThome

為了在儲存單元記錄更多資料,QLC快閃記憶體的讀寫機制先天上更為複雜與緩慢,也更不可靠,對磨損更為敏感,進而形成可靠性、耐用性與效能方面的先天缺陷,也導致用戶對於QLC充滿疑慮。

但另一方面,快閃記憶體只是SSD裝置與儲存系統的一部分,因而QLC快閃記憶體本身的缺陷,都能透過SSD控制器、SSD儲存裝置與儲存陣列系統層級的不同管理與控制手段,而得到緩解,從而讓用戶獲得QLC在降低成本、提高儲存密度方面的優點,又能迴避QLC可用性、耐用性與效能方面的不足。

要理解QLC種種問題的由來,以及克服這些問題的方法,必須先對NAND快閃記憶體的基本構造與運作方式,有一定理解,我們先解釋QLC固有問題的由來,然後再介紹解決這些問題的手段。

QLC快閃記憶體的固有問題

先天上,NAND快閃記憶體就存在著寫入抹除磨損、讀取干擾(Read Disturbance)、寫入干擾(Program Disturb),以及資料保持(Data Retention)等問題,這些狀況大都與快閃記憶體儲存單元氧化層的磨損有關。

在快閃記憶體儲存單元中,氧化層提供了絕緣、隔離的作用,讓浮動閘內的電荷不會輕易地逸散,即便斷電也能保存資料,實現「非揮發性儲存」的能力。但氧化層的隔離作用並不是絕對的,只要在控制閘或源極施加足夠的電壓,便能吸引電荷藉由穿隧效應穿透氧化層,進入或排出浮動閘,達到寫入與抹除資料的目的。

氧化層對於快閃記憶體的可靠性與壽命,有著決定性的影響。隨著抹除與寫入次數的增加,會給氧化層帶來不可逆的副作用:

當抹除與寫入次數增加後,電荷在浮動閘與底層矽基板間的進進出出,會讓浮動閘下方的氧化層逐漸「磨損」或「老化」,導致絕緣效果減弱(實際上是氧化層的化學鍵退化,造成絕緣能力減弱)。而當氧化層磨損後,會導致部分通過的電荷滯留在氧化層,同時也因絕緣效果減弱,讓浮動閘更難以留住電荷,電荷更容易流失,造成儲存單元的閾值電壓逐漸偏移,偏移量越大、就越難以正確判讀位元狀態。

而QLC的特性又進一步加劇前述的問題,事實上,QLC最大優勢——更高的儲存密度,正是一連串問題起因。

快閃記憶體是以電壓狀態來表徵儲存單元的位元狀態,TLC、MLC與SLC每個儲存單元雖然只記錄3個、2個與1個位元,但分別也只須控制8種、4種與2種電壓狀態,相較下,QLC每個儲存單元能記錄4個位元的資料,儲存密度更高,但連帶也需要區分與控制16種閾值電壓狀態,給QLC帶來更複雜、困難的存取程序,並最終導致抹寫耐用性更差,更困難的讀取作業與資料保存,以及更不可靠的寫入程序等問題。

更低的抹寫耐用性

QLC為人詬病的頭號問題,便是遠低於TLC、MLC與SLC的寫入與抹除壽命,但這個問題,其實是儲存單元氧化層磨損與閾值電壓偏移所導致。

如同前面提到的,快閃記憶體寫入抹除次數增加後,會有氧化層老化磨損與閾值電壓偏移的現象。對於SLC來說,閾值電壓只需維持2種狀態,2種電壓狀態可以區隔的很遠,即便出現較大幅度的閾值電壓偏移,也仍能很容易地判別儲存單元的位元狀態,所以SLC可容許更多次的抹寫循環,而無需顧慮由此帶來的閾值電壓偏移。

相較下,MLC、TLC與QLC為了記錄更多位元的資料,將閾值電壓區分為更精細、更多種的狀態,不同電壓狀態彼此更為接近,所以對閾值電壓的偏移容許幅度越小,而解決這個問題的辦法,就是限制儲存單元的寫入與抹除次數,藉此減緩氧化絕緣層的磨損,從而抑制閾值電壓偏移的程度。

舉例來說,TLC須控制與量測8種閾值電壓狀態,對儲存單元電壓狀態的變化,較只需控制4種電壓狀態的MLC更為敏感,因而對寫入與抹除次數的限制也更大;而QLC須控制多達16種電壓狀態,對儲存單元的電壓狀態變化又較TLC更為敏感,只要出現少許閾值電壓偏移,就會干擾與影響到位元狀態的判讀,因而也必須進一步限制抹除次數,以減少絕緣層磨損與閾值電壓偏移。

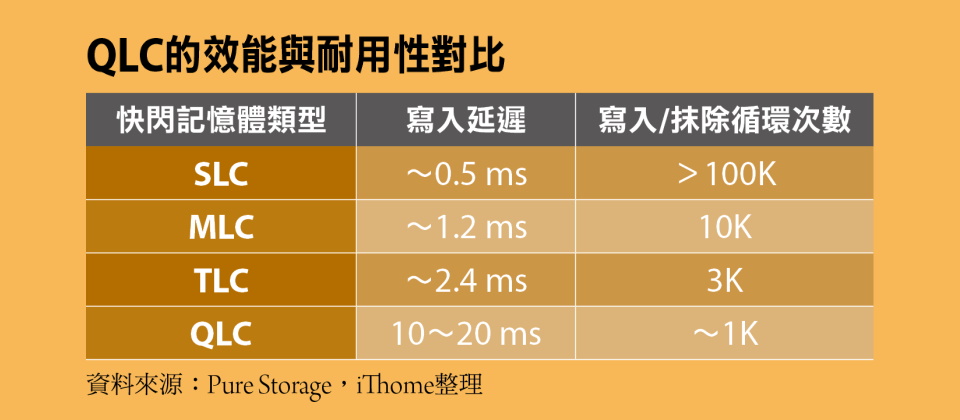

這也就是SLC、MLC、TLC與QLC不同耐用性與寫入壽命的由來。以寫入/抹除循環(Program Erase Cycle,P/E Cycle)計算,SLC快閃記憶體可允許10萬次以上,MLC降到1萬次,TLC又降到3,000次左右,而QLC更進一步降到1,000次以下,只有TLC的1/3不到。

更容易受干擾的讀取作業

QLC快閃記憶體的讀取作業,先天就更為複雜與緩慢。

隨著NAND快閃記憶體儲存單元的閾值電壓狀態區分越多、越精細,讀取程序將會越複雜,越緩慢。SLC每個儲存單元只有2種狀態,只需施加1個讀取電壓就能判別狀態。MLC每個儲存單元有4種狀態,必須依序施加3個參考電壓,才能完整判讀出儲存單元狀態。依此類推,QLC需要依序施加15個參考電壓才能完整判讀儲存單元的狀態,所以讀取作業先天上就更為複雜與緩慢。

除了讀取程序複雜外,QLC還有讀取更不精確、更易受干擾的問題。

NAND快閃記憶體是透過量測儲存單元的閾值電壓狀態,來判斷資料位元狀態,因此儲存單元維持閾值電壓狀態的能力,直接影響到資料讀取的正確性。

除了氧化層老化磨損導致閾值電壓偏移外,NAND快閃記憶體的讀取運作過程,也會造成儲存單元預期外的閾值電壓偏移,進而導致判讀位元狀態出錯。

快閃記憶體的讀取作業是以分頁(Page)為單位,如果要讀取某個分頁的資料時,需要對該分頁所在區塊(Block)的字元線(Word-Line)施加導通電壓,並對被選取的分頁施加參考電壓。而這也造成除了被選取的分頁之外,鄰近的分頁也都會被施加電壓,可能導致少許電荷被吸入這些鄰近分頁儲存單元的浮動閘,形成「輕微的寫入」,讓這些儲存單元的閾值電壓「悄悄地」增大,長此以往,便會導致這些儲存單元閾值電壓逐漸累積增大,造成位元狀態翻轉,變成「真正的寫入」,形成錯誤資料,這就是讀取干擾——為了讀取選定的儲存單元,卻影響、連累鄰近的儲存單元狀態。

讀取干擾會導致儲存單元閾值電壓逐漸變大,偏移出原本的範圍,如果控制器仍依照原本的閾值電壓範圍,去判讀儲存單元狀態,必然會發生誤判,以致讀取錯誤。而儲存單元閾值電壓偏移的幅度,則與讀取次數有關——讀取次數越多,偏移越大。

透過Refresh程序——也就是先讀出資料、經ECC修正後再將資料重新寫回到另一區塊,並抹除原有區塊資料,可修正讀取干擾的問題,但這項作業會影響效能,還需趕在讀取干擾超過ECC修正能力之前,就完成Refresh作業。

在SLC與MLC時代,對閾值電壓偏移容忍程度較高,因而讀取干擾屬於學術性問題,還不致對現實作業帶來困擾。

不過,到了TLC崛起之後的時代,隨著閾值電壓狀態增加到8種,電壓區間被分為更精細的8份,不同狀態的電壓彼此更為接近,讀取干擾開始成為要擔心的問題,而到了必須區分16種閾值電壓狀態的QLC時代,這更成為一個不妥善處理就會成為災難的問題。

更不可靠的資料寫入程序

QLC快閃記憶體的寫入作業,同樣也是先天上就更為複雜與緩慢。

因為NAND快閃記憶體是透過向儲存單元控制閘施加寫入電壓,藉此向浮動閘注入不同數量的電荷,改變儲存單元的閾值電壓,讓儲存單元呈現不同的位元狀態,達到寫入資料的目的。

而QLC儲存單元具備多達16種閾值電壓狀態,必須更為緩慢與仔細地控制寫入電壓與寫入程序,才能確保正確寫入資料,難度比起SLC、MLC、TLC可說是指數性的增加,這也導致QLC的寫入延遲遠高於SLC、MLC與TLC。

根據快閃儲存陣列供應商Pure Storage提供的資料顯示,SLC的寫入延遲低於0.5 ms,MLC約為1.2 ms,TLC也還有2.4 ms左右,相差都不大,而QLC的寫入延遲便大幅拉長到10到20 ms,整整增加了10倍。

NAND快閃記憶體的寫入也有寫入干擾問題。向某個分頁執行寫入作業時,除了被選中寫入的儲存單元外,同一條字元線上的鄰近儲存單元電壓也會跟著升高,導致輕微寫入,最終導致這些被干擾的儲存單元位元狀態翻轉,成為錯誤資料狀態。隨著QLC儲存單元的電壓狀態區分越多、越精細,這個問題的影響也更嚴重。透過Refresh同樣能修復寫入干擾,但連帶也有影響效能的問題。

更低的資料保持能力

隨著抹除次數增加,快閃記憶體儲存單元氧化層磨損導致絕緣效果減弱,會造成浮動閘更不易保存電荷,隨時間逐漸洩漏,儲存單元電壓也逐漸降低,到達一定限度後,將導致資料遺失。事實上,即便抹寫次數很少,靜置的快閃記憶體儲存單元,也會慢慢洩漏電荷,所以,快閃記憶體雖被歸類於無須供電也能保存資料的「非揮發性」儲存媒體,但其保存資料的能力是有期限的。

作業環境溫度與寫入與抹除循環次數(P/E),是影響NAND快閃記憶體資料保存能力的兩大因素。

溫度升高將會加劇儲存單元中的電荷運動與振動,使其更容易穿透氧化層,加劇浮動閘的漏電現象,在攝氏50度以上便會有顯著影響,導致資料保持時間大幅衰減。

依照快閃記憶體產品製造商宜鼎的資料,當溫度從40到50度區間升高到50到60度區間,快閃記憶體資料流失速度將提高10倍,保存資料的期限大幅降低,若溫度進一步升高到60到70度間,資料流失速度更將提高30倍。而QLC對儲存單元的閾值電壓變化更為敏感,連帶也對高溫更敏感。

更多的抹寫次數,則會導致與氧化層更嚴重的磨損,當磨損越大,電荷越容易從浮動閘中洩漏,導致資料遺失。因而快閃記憶體的資料保持時間(retention)長短,與寫入/抹除次數成反比。隨著抹寫次數增加,有效的資料保持時間變得越短,這對於抹寫壽命較短的QLC也更為不利。透過Refresh雖能延長保存時間,但也有其副作用。

克服QLC弱點的手段

QLC快閃記憶體的種種問題,是先天的運作架構所致,難以在儲存單元或區塊這個層級解決,但可以透過SSD裝置層級,或儲存系統層級的管理手段,來克服或緩解。

既有MLC、TLC SSD產品用於改善耐用性、可靠性與效能的技術,如超額容量配置(Over-Provisioning)、損耗均衡(Wear-Leveling)與故障區塊管理(Bad Block Management),預防性Refresh與資料搬離(Early Move),以及ECC錯誤修正校驗等等同樣也能用於改善QLC SSD產品的耐用性、可靠性與效能。

但由於QLC比MLC、TLC更不可靠、更不耐用,所以單單只是沿用既有錯誤修正與故障區塊處理機制,仍不足以克服QLC問題,必須予以進一步增強。目前被採用的改善方式,涵蓋了從製程、控制器與SSD裝置等多個面向:

● 記憶體製程層級

在記憶體製程方面,常見的改良手段,是透過3D堆疊技術搭配較老的製程(如40nm),設法讓QLC能兼顧耐用性與儲存密度。使用較老的製程雖然會增加快閃記憶體單元的尺寸,但可讓獲得物理上較厚、也較耐磨損的氧化層,再結合3D堆疊技術來提高儲存密度,彌補較老製程所損失的儲存密度。

另外,再結合浮動閘與氧化層材料的改進,也改善了保存電荷與絕緣能力,有助於提高QLC的耐用性。

● SSD控制器層級

在SSD控制器方面,針對QLC更不可靠的存取,一些SSD控制器廠商發展了專門針對QLC的LDPC(低密度奇偶校驗)錯誤修正演算法,提高存取錯誤修正能力;另外還結合了動態區塊掃描功能,可視風險程度提高區塊掃描頻率,更頻繁地檢測各區塊的狀況,及早修正有風險的區塊,並更積極、更頻繁地執行Refresh,與替換潛藏問題的區塊。

● SSD裝置層級

在SSD裝置方面,則能利用模擬SLC模式,與更高的超額容量配置,來改善QLC效能與耐用性。

透過SLC模擬模式來改善效能,早在TLC SSD上便已廣獲採用,QLC SSD自然也能跟進採用,例如三星的QLC SSD,便提供了稱作TurboWrite的SLC模擬寫入緩衝技術,Intel的QLC SSD也擁有SLC快取功能。

而所謂的SLC模擬模式,是將TLC與QLC SSD的部分空間或全部空間,模擬使用SLC的寫入模式,在每個儲存單元只記錄1個位元的資料,因而存取速度較標準的TLC與QLC模式快了許多,可作為讀取快取與寫入緩衝使用,加速SSD整體的存取效能,讓QLC SSD擁有不亞於TLC SSD的效能表現。

而在SSD上採用更高比例的超額容量配置,利用預留更多的備用區塊,作為磨損區塊的替補,可大幅減緩QLC SSD整體的磨損,延長使用壽命。

前述改善方式,都已普遍被應用在當前QLC SSD產品上,並取得顯著的成效,相較於5年前問世的第一代QLC SSD,新一代QLC SSD的耐用性提升近一倍——以總寫入資料量(TBW)為基準,存取效能則提高50%以上。

但另一方面,這些改進方式也各有其代價,例如,採用增強的ECC演算法、更頻繁的掃描區塊,都會給SSD控制器帶來更高的處理負荷與功耗。模擬SLC模式的快取機制,則會增加特定區域的抹寫損耗(使用部分空間作為SLC快取),或是減損整體的儲存密度(使用全部空間作為SLC快取),需要超額容量配置來彌補。更頻繁的Refresh與預防性搬移資料,會在背景耗用更多資源,影響SSD效能,並需要占用更多額外區塊空間,同樣需要超額容量來抵銷。

多數SSD都提供7%的超額容量配置,一些強調寫入應用的企業級SSD甚至提供了20到25%的超額容量配置。然而,超額容量是以成本為代價,越高比例的超額容量配置,成本也越高,如果因此造成QLC SSD成本過高,反而本末倒置,失去導入QLC的初衷。

對此,率先將QLC應用於企業級儲存陣列的Pure Storage,認為不應過於依賴超額容量配置來解決QLC的問題,他們表示,透過結合從儲存模組到儲存陣列的一系列管理與控制機制,將能更有效改善QLC的固有弱點。

儲存陣列層級的解決方案

大多數用於克服QLC問題的手段,都是在SSD控制器與SSD裝置層級進行。

而儲存陣列廠商則能從儲存陣列系統層級,提供其他的解決方式。

例如Pure Storage的快閃儲存陣列QLC解決方案,便利用儲存陣列層級的快取與緩衝,來緩解QLC的問題,例如藉此讀取快取來減緩QLC的讀取干擾,利用緩衝記憶體來幫助改善寫入作業的可靠性,還會藉由將metadata盡可能快取到快取記憶體中,不需要在底層QLC快閃記憶體儲存模組上存取metadata,藉此迴避QLC的效能問題,並減少磨損。

除了Pure Storage以外,Dell、StorOne等儲存陣列廠商,在使用QLC時也都採取類似的存取架構,透過儲存陣列層級的緩衝記憶體,來輔助資料寫入作業,藉此避開QLC的寫入效能問題。

以往機械式硬碟當道的時代,為了填補硬碟與處理器之間的效能與延遲落差,快取與緩衝記憶體是儲存陣列最關鍵的環節之一,透過優化快取演算法,提高快取命中率,盡可能讓快取來回應讀取負載,而無須到底層硬碟上讀取資料;寫入時則由緩衝記憶體來承接與回應寫入負載,然後在背景將寫入區塊累積成固定的大小,再循序寫入硬碟,藉此不僅能以記憶體等級的速度來回應寫入需求,還能將隨機小區塊寫入,轉為循序大區塊寫入,迴避硬碟不擅長隨機寫入的弱點。

到了全快閃儲存時代,由於SSD存取速度遠高於硬碟,快取與緩衝的作用便不像以前那樣顯著,即便快取沒有命中,直接讓讀取負載落入底層SSD,或是不經緩衝記憶體,直接讓寫入負載進入SSD,儲存陣列整體也仍然能擁有足夠高的效能,藉此還能節省讀取快取在昂貴DRAM中的占用量,或是節省更為昂貴、由NVRAM構成的寫入緩衝區。

然而隨著快閃儲存進入QLC時代,QLC同樣是延遲較大、且不擅長隨機寫入的儲存媒體,快取與緩衝記憶體的作用,也可望重新抬頭。如果可以妥善利用儲存陣列的快取與緩衝記憶體,將能相當程度地迴避與緩解QLC的弱點。

對讀取作業來說,只要快取命中率夠高,大多數讀取負載都將落在快取,前端將能得到快取記憶體等級的讀取回應速度,可減少讀取底層QLC SSD頻率,QLC SSD將不致影響儲存陣列整體的回應速度,同時也減緩讀取干擾問題。

而對寫入作業來說,由緩衝記憶體先行承接寫入負載,後續再於背景將寫入I/O實際寫入底層QLC SSD ,只要緩衝記憶體夠大,前端將能得到記憶體層級的寫入效能,同時也迴避QLC SSD的隨機寫入效能弱點。

因而我們認為,一些強調高效率快取與緩衝機制的儲存陣列平臺,在QLC時代將大有可為,既可利用QLC降低成本,同時又迴避QLC效能與耐用性問題。藉由這種架構,QLC不僅能用於一般企業環境,高效能領域也不成問題。

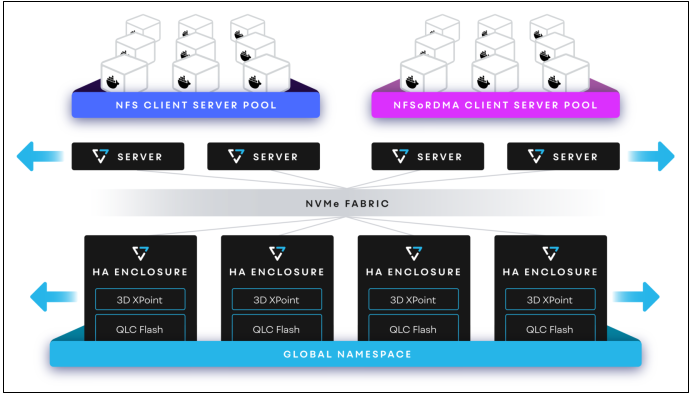

VAST Data的Universal Storage平臺便是一個例證,同時結合了高效能的儲存級記憶體(SCM),以及低成本的QLC SSD,利用SCM作為存取緩衝與存放metadata,QLC SSD則用於最終的資料儲存。所以儘管VAST Data底層架構是基於QLC SSD,整個平臺卻是定位於高效能運算的儲存應用,打破一般認為QLC不適合高效能應用的刻板印象。

不過,也有部分廠商持相反的看法,例如Infinidat與HPE。

Infinidat與HPE旗下的Nimble產品線,都以高效率快取機制著稱,Infinidat的神經快取演算法(neural caching)號稱擁有當前市場上最高的快取命中率,寫入快取通常為100%,讀取快取也達到93%至99%;HPE Nimble的快取加速循序布局(CASL)技術,則宣稱只需4%的快取容量比率,就能實現90%快取命中率,8%快取容量比率就能達到近100%快取命中。

所以Infinidat與HPE Nimble過往都宣稱,他們只須採用SSD搭配硬碟的混合架構,就能提供同等甚至超過全快閃陣列的效能,絕大多數I/O都落在快取層,不會直接進入底層硬碟。依循相同思路,QLC在Infinidat與HPE Nimble架構中,應該也能得到很好表現。

但Infinidat與HPE同樣以QLC還不夠便宜的理由,否定引進QLC的必要,認為維持使用硬碟更具成本效益。

不過我們也要注意,Infinidat與HPE發表否定QLC言論時間是2019與2021年,隨著QLC製程的進步,不僅成本終將降低到足以與硬碟相比的程度,儲存密度更將提升到硬碟遠遠無法比擬的層次,單一SSD就擁有100TB容量時代,很快就會到來,屆時這兩家廠商恐怕最終還是必須接受QLC——就像他們過去也曾否定全快閃組態的必要,認為以混合陣列就足以滿足用戶的效能需求,但最終還是抵擋不了市場趨勢,而推出全快閃組態產品。

QLC問題的根源:儲存密度與可靠性的兩難

SLC是透過2種電壓狀態來表徵1個位元狀態,2種電壓狀態的區間相隔很遠。MLC則使用4種電壓狀態來表徵2個位元狀態,電壓區間被分為更細的4等分,不同狀態的電壓差也縮小許多。TLC又進一步以8種電壓狀態來表徵3個位元狀態,不同狀態的電壓差再度縮小。

到了QLC,電壓狀態增加到16種,用於表徵4個位元狀態,雖然提高資料儲存密度,但各個不同狀態的電壓差也縮到更小,因而讀取與寫入的電壓控制更為困難,對閾值電壓偏移更為敏感,少許電壓偏移,就會干擾到存取正確性,連帶也對儲存單元的氧化層磨損更為敏感,必須大幅限縮儲存單元抹寫次數,來抑制氧化層磨損帶來的閾值電壓偏移幅度。圖片來源/AnandTech

.png)

QLC的效能與耐用性對比

較大的寫入延遲,以及更低的耐用性,是QLC為人詬病的2大缺陷。

目前主流的TLC快閃記憶體,寫入延遲與耐用性雖然低於MLC,但差距只有2、3倍。而QLC的延遲與耐用性,卻又比TLC更低了好幾個層次,寫入延遲大了5到10倍,耐用性則只有TLC的1/3。資料來源:Pure Storage,iThome整理

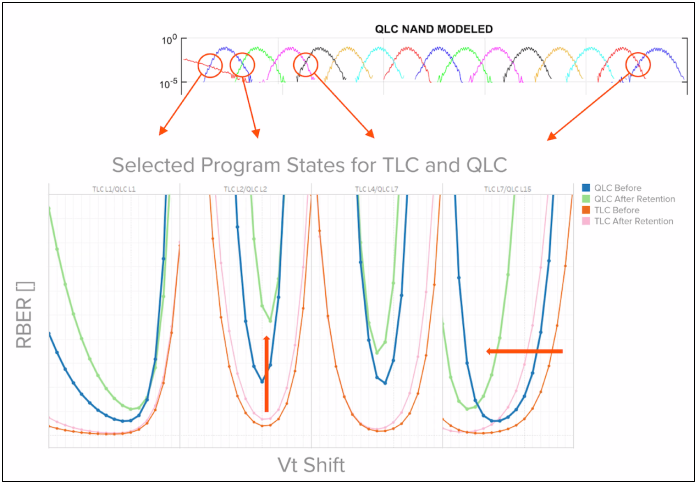

QLC的讀取問題

更困難的資料讀取過程,是影響QLC效能的原因之一。根據這張Pure Storage提供的圖表顯示,QLC的原始位元錯誤率(RBER)明顯比TLC更高,抹寫磨損後的閾值電壓偏移也更大,這意味著QLC的讀取更不可靠,需要強度更高的ECC機制來修正錯誤。圖片來源/Pure Storage

透過快取與緩衝緩解QLC效能問題

在儲存陣列層級,若能妥善利用快取與緩衝記憶體作為讀寫負載的中介,將能相當程度迴避與緩解QLC的弱點。VAST Data的架構便是典型,利用SCM作為存取緩衝與存放metadata,QLC SSD則用於最終的資料儲存,利用SCM來提高效能,並搭配QLC來降低儲存成本。圖片來源/VAST Data

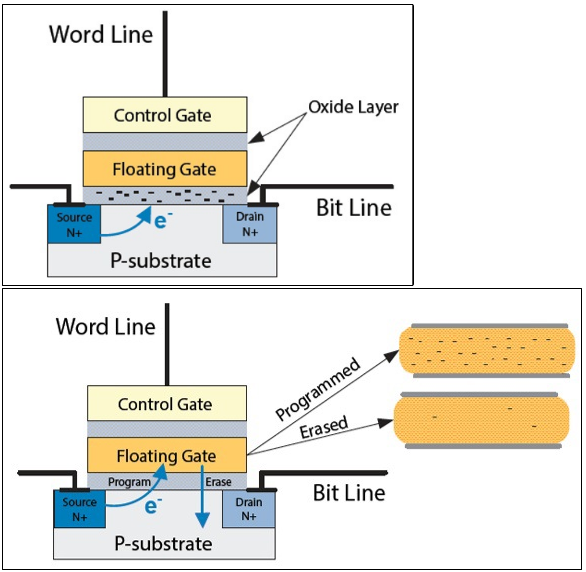

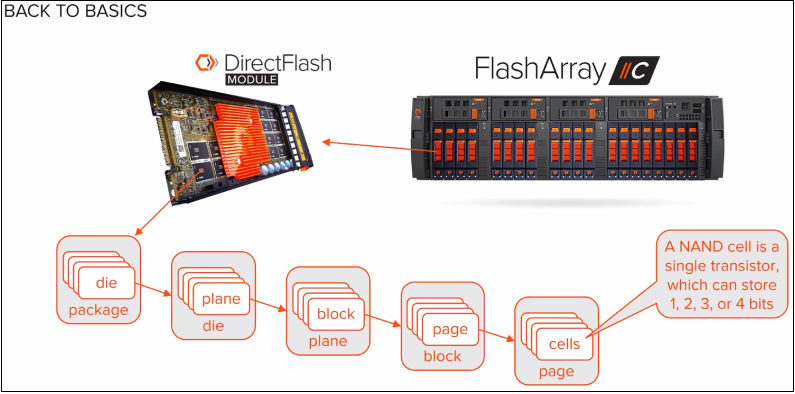

NAND快閃記憶體的基本運作

NAND快閃記憶體的基本儲存單元(Cell),是由浮動閘(floating gate)、控制閘(Control gate),上下包夾住浮動閘的氧化層(Oxide Layer),加上源極(Source)與汲極(Drain),以及底層矽基板組成的電晶體(transistor),其中,控制閘與浮動閘連接著字元線(Word-Line),源極則透過位元線(Bit-Line)與鄰接儲存單元的汲極連通。

而不同儲存單元再藉由字元線與位元線的連通,構成一個矩陣的結構。同一條字元線串聯多個儲存單元組成分頁(Page),這是讀取與寫入作業的基本單位;多個分頁再組成區塊(Block),這是抹除作業(Erase)的基本單位。

而透過字元線與位元線來控制施加給儲存單元的電壓,便能讓儲存單元進行寫入、讀取與抹除等3項存取作業。

向儲存單元寫入資料的動作稱為編程(Programming),藉由控制閘施加電壓,將電荷(electrical charge)從底層矽基板吸入浮動閘,浮動閘則藉由捕獲與蓄積電荷,來改變儲存單元的閾值電壓(Threshold voltage,Vt)。

控制閘施加的不同電壓,會影響穿過氧化層、進入浮動閘內的電荷數量,進而讓儲存單元擁有不同的閾值電壓,代表儲存單元的位元狀態。

而要讀取儲存單元中的資料時,則藉由控制閘施加不同的參考電壓,來量測源極與汲極間的電流,從而判斷浮動閘內蓄積的電荷量,從而判讀出儲存單元的位元狀態。

而要抹除儲存單元中的資料時,則是向源極施加電壓,將浮動閘內的電荷吸出、穿過氧化層,排放到底層矽基板中。

NAND快閃記憶體儲存單元基本構造與運作

利用浮動閘(Floating Gate)內保存的電荷來紀錄資料,並透過在控制閘(Control Gate)與源極(Source)施加電壓,來控制電荷在浮動閘與矽基板(P-substrate)間的流動與進出,從而達到寫入、抹除與讀取資料的目的。上下包覆住浮動閘的氧化層(Oxide Layer),則能將電荷拘束在浮動閘中,防止電荷逸散出去。

快閃記憶體的資料寫入作業,就是將電荷從矽基板吸入到浮動閘,抹除作業則是將電荷從浮動閘中排出,而讀取作業則是藉由量測浮動閘內保存的電荷數量,來判定資料位元狀態。圖片來源/Western Digital

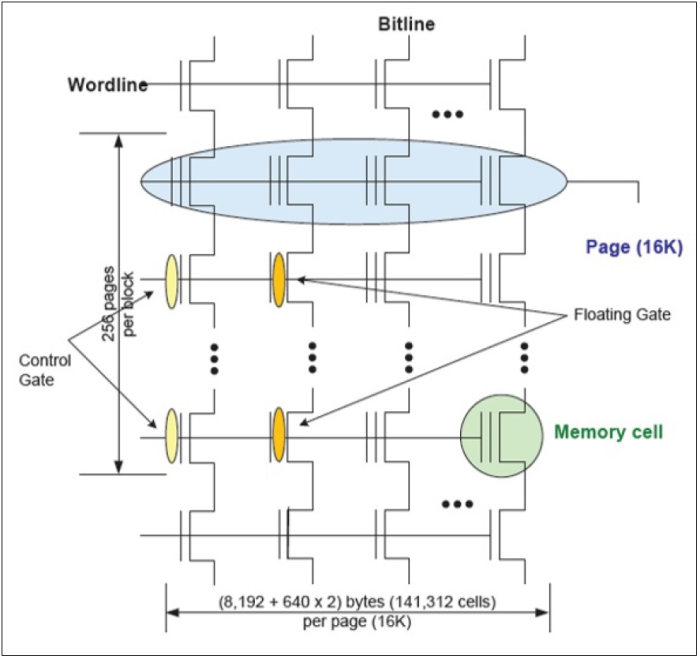

NAND快閃記憶體分頁與區塊組成

NAND快閃記憶體是以儲存單元(Cell)作為基本組成單元,然後多個儲存單元再透過字元線(Word-Line)與位元線(Bit-Line),彼此串聯成為矩陣結構。

以左圖為例,4個4K的儲存單元,利用字元線串聯成一個16K的分頁(Page),這NAND是快閃記憶體執行資料讀取與寫入作業的基本單位。

然後,以256個分頁再組成1個4096K的區塊(Block),這是NAND快閃記體執行資料抹除作業的基本單位。圖片來源/Western Digital

Pure Storage的QLC解決方案

在2020年Storage Field Day 20研討會影片中,我們看到Pure Storage的工程副總裁暨首席硬體架構師Pete Kirkpatrick,介紹該公司基於QLC的儲存陣列產品FlashArray//C系列時,也說明了該公司解決QLC問題的一系列方法。

記憶體製造商與SSD廠商,是在快閃記憶體製程、SSD控制器與SSD裝置層級,來設法改善QLC的弱點。儲存陣列廠商則是從儲存系統層級,來著手緩解QLC的問題。

而Pure Storage則同時結合了從快閃儲存模組到儲存陣列層級的一系列手段,來克服QLC的先天缺陷。

首先,Pure Storage並不採用一般的SSD,而是採用該公司特製的DFM儲存模組,並沒有一般SSD所普遍內建的FTL層,由儲存陣列控制器運行的Purity儲存作業系統,直接控制DFM模組上的快閃記憶體單元,並執行原本由FTL層負責的空間映射、錯誤校正、寫入均衡等背景管理功能。

Pure Storage宣稱透過專門設計的DFM模組,既可降低延遲、提高效能,由於DFM不執行垃圾收集作業,也能大幅減少寫入放大,而有助於提升QLC的耐用性與效能表現。

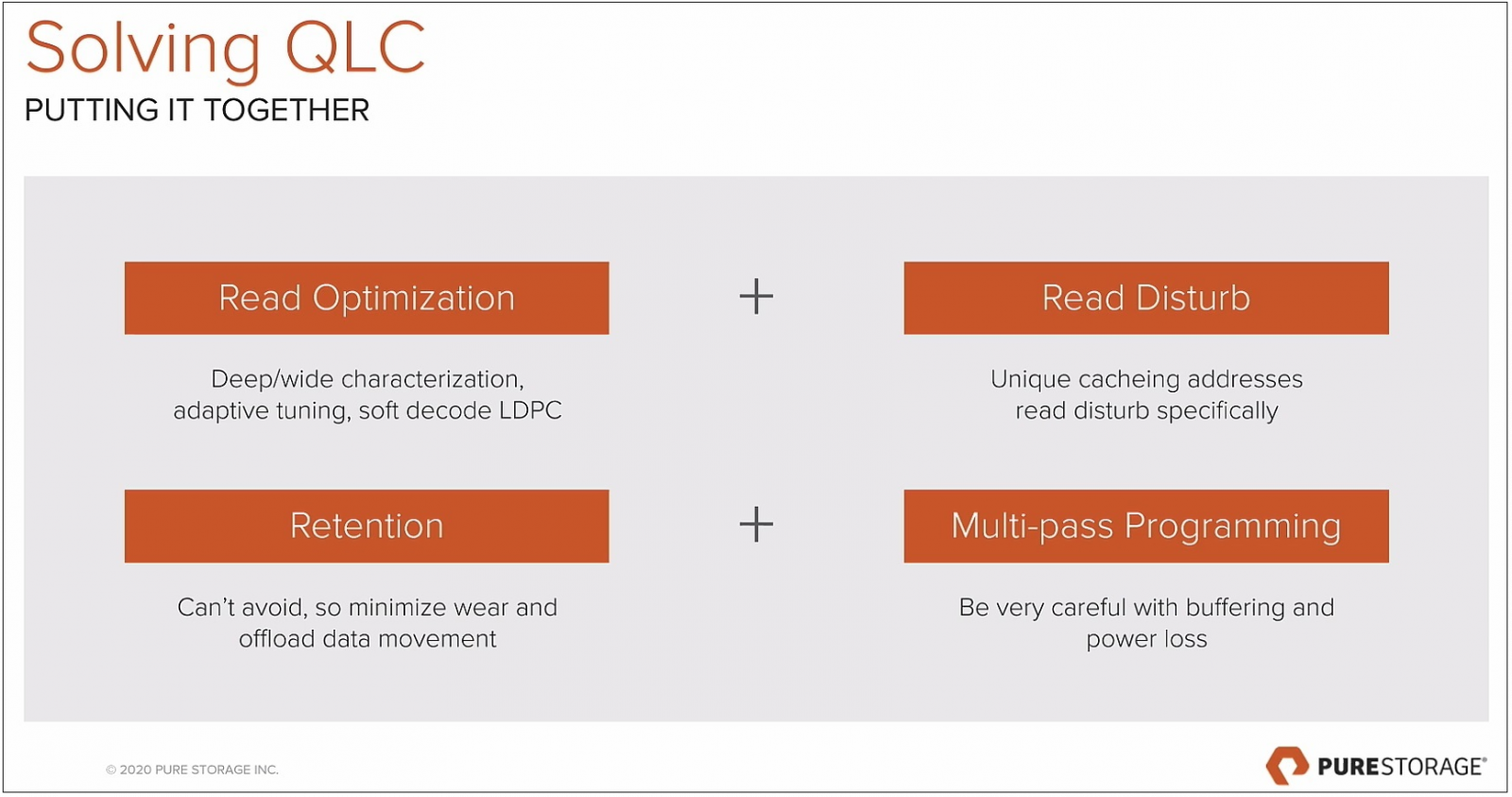

其次,針對QLC面臨的讀取可靠性、讀取干擾、資料保存、寫入可靠性等問題,Pure Storage採取了下列因應措施:

● 改善讀取正確性的讀取最佳化

為了因應QLC更嚴重的閾值電壓偏移,儲存狀態更大的變化、更高的原始位元錯誤率(Raw Bit Error Rate,RBER),導致讀取困難的問題,Pure Storage採用更深、更廣的存取特性描述(Deep/wide characterization),結合適應性調整(adaptive tuning)技術,以及軟體式LDPC解碼,來改善QLC的讀取效率。

Pete Kirkpatrick當時並沒有進一步解釋這些技術的運作方式,依據我們的推測,應該是藉由更深、更廣的存取特性描述,搭配適應性調整技術,來收集更多的存取狀態資訊,從而計算出最佳的讀取電壓,可因應QLC更嚴重的閾值電壓偏移,提高讀取成功的機率,減少反覆讀取嘗試導致的延遲。

至於由儲存陣列控制器執行的軟體LDPC,則是Pure Storage慣用的做法,雖然速度較慢,但可以獲取更多的存取狀態資訊,更仔細、更有效的糾正讀取錯誤,提高讀取成功的機率。

● 減緩讀取干擾

透過專門針對讀取干擾問題而設計的快取機制,盡可能從快取讀取資料,減少讀取底層QLC快閃記憶體的次數,從而減緩讀取干擾的發生。

● 改善資料保持壽命

Pure Storage的基本原則是盡可能減少磨損,並將資料搬移卸載到儲存模組層級。

● 多重寫入

針對QLC更不可靠的寫入機制,Pure Storage採用搭配緩衝區的多重寫入程序(Multi-pass programming),確保資料被正確的寫入底層QLC。

Pure Storage的QLC解決方案

Pure Storage採用了4種方法,提升QLC的效能與可靠性,包括:改善讀取正確性的讀取最佳化,緩解讀取干擾的快取機制,提高資料保存期的減緩磨損與資料搬移損耗技術,還有改進寫入正確性的多重寫入技術。圖片來源/Pure Storage

基於專屬DFM模組的QLC應用架構

在FlashArray//C儲存陣列上,Pure Storage結合從儲存模組到儲存陣列的一系列手段,以此來克服QLC快閃記憶體面臨的各種先天限制。最特別的是,他們在自家的產品當中,使用了沒有FTL層的專屬DFM儲存模組,由儲存陣列控制器運行的Purity作業系統,直接控制DFM模組上的快閃記憶體存取。圖片來源/Pure Storage

熱門新聞

2023-12-03

2024-04-24

2024-04-25

2024-04-26

2024-04-26

2024-04-25

2024-04-22

.PNG)